# **Cloud FPGA** • $\bullet$ **EENG 428** ENAS 968 •

# bit.ly/cloudfpga

### **Lecture: Behavioral Modeling**

# Prof. Jakub Szefer Dept. of Electrical Engineering, Yale University

## EENG 428 / ENAS 968 Cloud FPGA

This lecture is mostly based on contents of Chapter 3, from "The Verilog Hardware Description Language" book [1], 5<sup>th</sup> edition. Example figures and (modified) code are from the textbook unless otherwise specified.

#### **Topics covered:**

- Blocking and non-blocking assignments

- Behavioral modeling with processes

- If-then-else, if-else-if, case statements

- Functions and tasks

- Structural view

- Rules of scope and hierarchical names

Foreshadowing of chapter 8:

- The <= operator is allowed anywhere the = is allowed in procedural assignment statements

- The non-blocking assignment operator cannot be used in a continuous assignment statement

- Don't use in assign statements

- Don't confuse with less-than-equal <=</li>

- Going left-to-right in an expression, first <= is assignment, others are comparisons</li>

- Non-blocking behavior, the <= does not block the process:

#### Style-guide:

- Use non-blocking in sequential logic, always @ (posedge clock)

- All others (combinatorial logic, functions, tasks) use blocking

Using = here can possibly lead to extra storage elements being synthesized, affecting timing of circuit

#### **Behavioral Modeling and Processes**

........

#### Processes

- tomonts

- A process is described in Verilog using **always** statements and **initial** statements

- The always process continuously repeats itself

- The initial statement only runs once (at start of simulation, for example)

- There can be many such statements in a module, which logically execute concurrently

- A module can also have none, in which case it only described structure of logic (e.g. connections between modules)

- The initial statements cannot be synthesized into hardware

- They are used for simulation to initialize values

- In synthesized hardware typically a 'reset' signal is used to initialize values

- For FPGAs, the tools usually let you set initial value for a register

- For ASIC need to explicitly reset all registers when system starts

```

// Initialize value with initial statement

reg myVal;

```

```

initial

begin

myVal = 1;

end

```

end

// Initialize value when defining a register

reg myVal = 1;

```

// Initialize value using reset signal

always @(posedge clock, posedge reset)

begin

if (reset)

myVal <= 1;

else

myVal <= ...;</pre>

```

EENG 428 / ENAS 968 – Cloud FPGA © Jakub Szefer, Fall 2019

7

#### Execution Model of always and initial

- Within each process, the statements are evaluated serially, similar to a set of C instructions

- When using blocking = values are assigned immediately and can be used in next statement

EENG 428 / ENAS 968 – Cloud FPGA

© Jakub Szefer, Fall 2019

- When using non-blocking <= the values are assigned in parallel</li>

- Event statements @, delay statements #, and wait statements cause the evaluation of the process to be suspended until, respectively:

- Event occurs

- Number of time units has passed

- Condition becomes true

- Event statements continue when condition is met

- The events, time delay, or conditions becoming true are triggers for statement evaluation to continue

Regardless, all always and initial work in parallel, there is no order of value updates

reaches the end

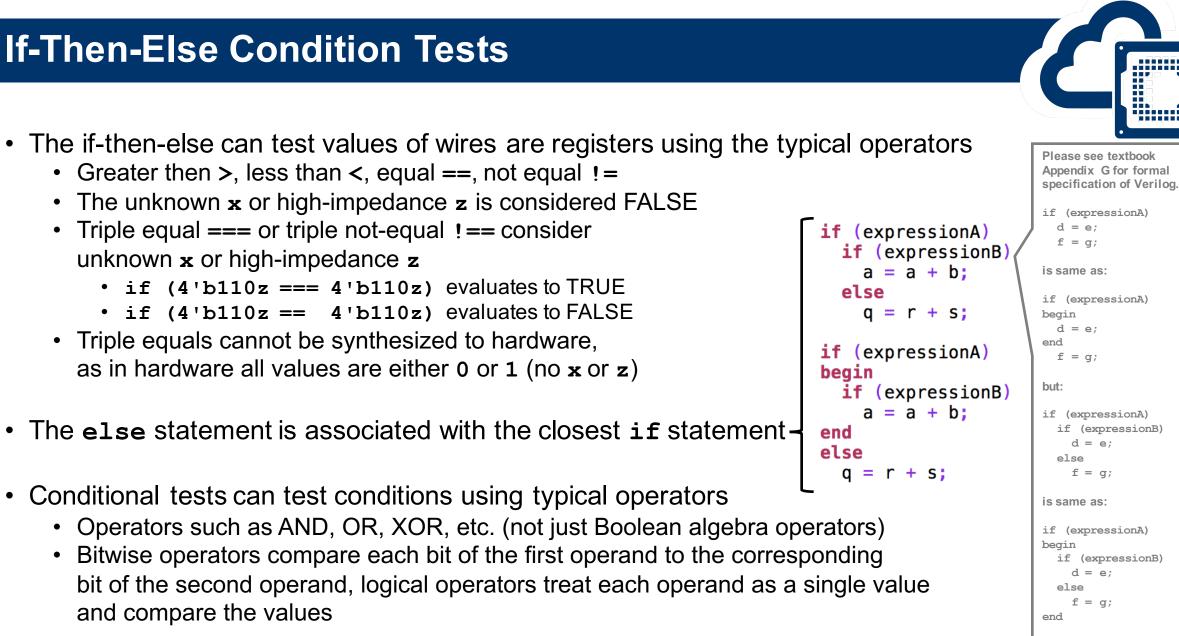

### **If-Then-Else Condition Tests**

Share: bit.ly/cloudfpga

#### Loops

Four different loop statements are available in Verilog:

- repeat ( numTimes )

- for ( initLoopCond; testExpression; updateLoopCond )

- while ( someCondition )

- forever

Condition needs to be updated in loop body, can't use external conditions, e.g. module inputs

parameters, or macros

Expressions or test conditions for the

Use integer values or registers with extra bits to avoid wrap-around when updating test condition

The loops will not be actually created in hardware, they are just used to describe the behavior of the system or module

- Will generate simple logic if each loop condition is independent and can execute in parallel

- May generate very complex logic if there are interdependencies between each loop iteration

Loops can be exited early using disable statement

• Similar to break statement in C

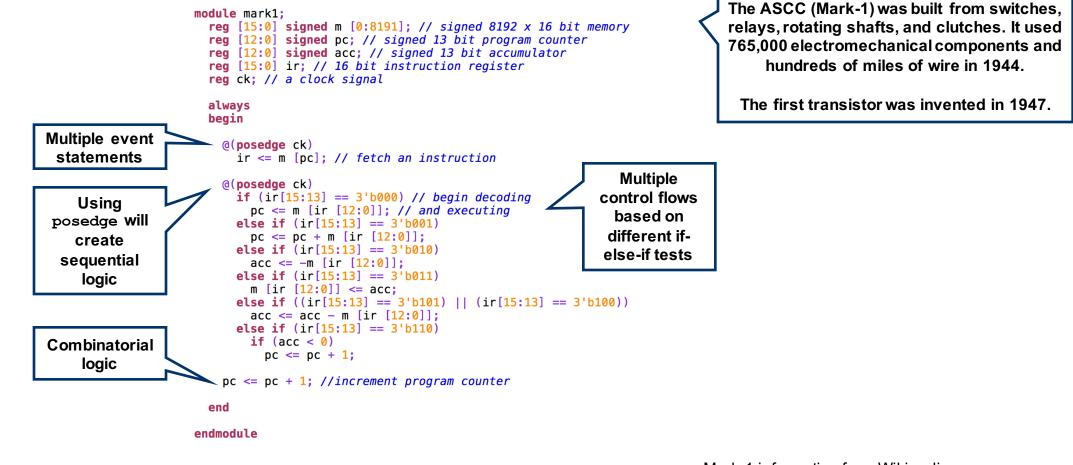

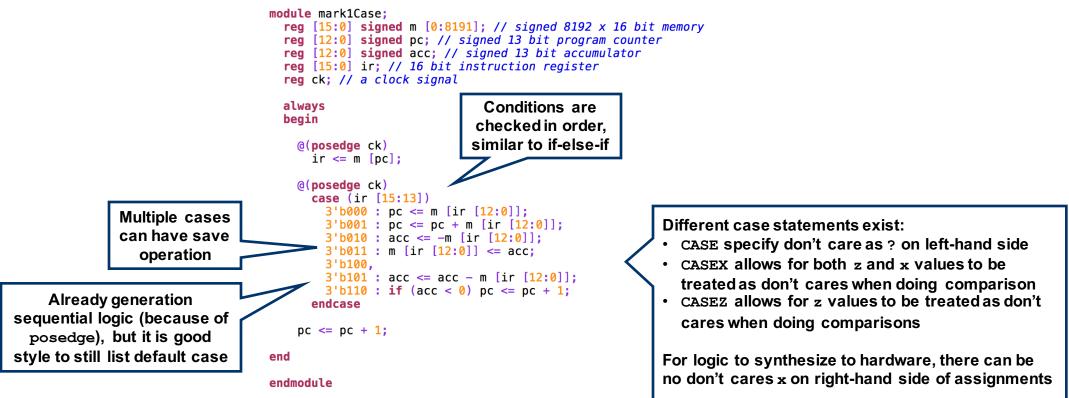

## **Multi-Way Branching**

- If-else-if statements and case selection statements allow for multi-way branching

- Example of code to emulate simplified Mark-1 processor

EENG 428 / ENAS 968 – Cloud FPGA © Jakub Szefer, Fall 2019

## **Multi-Way Branching**

- If-else-if statements and case selection statements allow for multi-way branching

- Example of code to emulate simplified Mark-1 processor

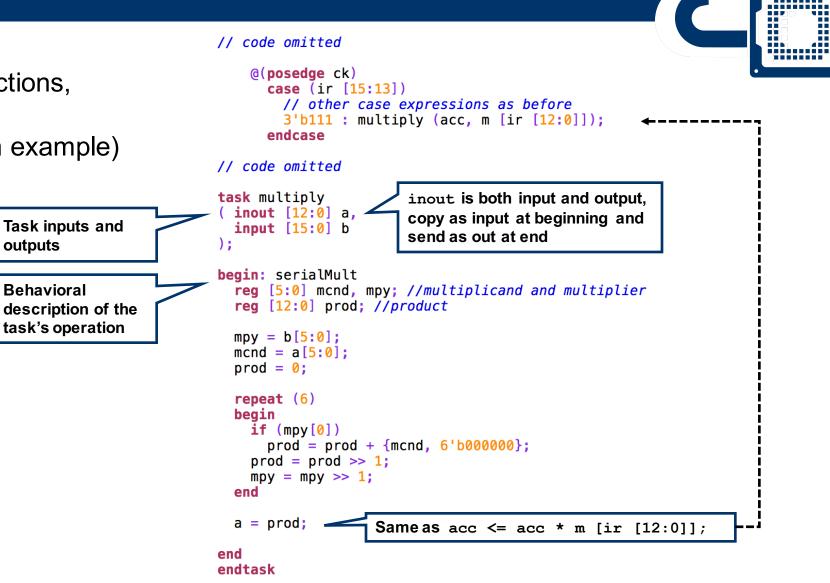

#### **Functions and Tasks**

#### **Functions and Tasks**

- Verilog provides functions and tasks as primitives similar to software functions

- They allow for the behavioral description of a module to be broken down into even moremanageable parts

- 1. First, break design into module hierarchical design

- 2. Second, use functions, tasks, macros, etc. in module further break down the complexity

- Functions and tasks can be written for often-used behavioral sequences, write the description once and then re-use many times

- Functions are simpler (less options) and can be used for synthesizing hardware

- Task are more complex, and mainly used for simulation

- Can't synthesize to hardware, e.g., when delay is used in a task

#### **Comparison of Functions and Tasks**

Comparison table from the textbook [1] shows the different features of functions and tasks

| Category                                        | Tasks                                                                                                                                                                                     | Functions                                                                                                                                                                                                                                          |             |                                                                                  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|

| Enabling (calling)                              | A task call is a separate pro-<br>cedural statement. It can-<br>not be called from a<br>continuous assignment<br>statement.                                                               | A function call is an oper-<br>and in an expression. It is<br>called from within the<br>expression and returns a<br>value used in the expression.<br>Functions may be called<br>from within procedural and<br>continuous assignment<br>statements. |             | •                                                                                |

| Inputs and outputs                              | A task can have zero or<br>more arguments of any<br>type.                                                                                                                                 | A function has at least one<br>input. It does not have<br>inouts or outputs. How-<br>ever, a value is returned.                                                                                                                                    |             |                                                                                  |

| Timing and event controls<br>(#, @, and wait)   | A task can contain timing<br>and event control state-<br>ments. Thus it can be con-<br>currently active if called<br>from concurrent always/ini-<br>tial blocks.                          | Functions may not contain<br>these statements. They are<br>not re-entrant.                                                                                                                                                                         | 7           | Not re-entrant,<br>recursive calls to<br>functions and tasks<br>use same storage |

| Enabling (calling) other<br>tasks and functions | A task may enable other<br>tasks and functions                                                                                                                                            | A function can enable other<br>functions but not other<br>tasks.                                                                                                                                                                                   | $  \rangle$ | Need to define as                                                                |

| Storage                                         | Storage of the inputs, out-<br>puts, and internally declared<br>variables is static — concur-<br>rent calls share the storage.                                                            | Storage of the inputs and<br>internally declared variables<br>is static. If the function is<br>declared automatic, then                                                                                                                            |             | automatic to allow<br>for recurrence                                             |

|                                                 | However, if the task is<br>declared automatic, then<br>the storage is dynamic and<br>each call gets its own copy.                                                                         | the storage is dynamic and<br>recursive calls get their own<br>copies.                                                                                                                                                                             |             | Non re-entrant have<br>static storage, re-<br>entrant have dynamic               |

| Values returned                                 | A task does not return a<br>value to an expression.<br>However, values written by<br>the task into its inout or<br>output ports are copied back<br>at the end of the task execu-<br>tion. | A function returns a single<br>value to the expression that<br>called it. The value to be<br>returned is assigned to the<br>function identifier within<br>the function.                                                                            |             | storage, may not<br>synthesize to<br>hardware                                    |

Tasks

Tasks are very similar to functions, but can set multiple outputs and use timing (not shown in example)

EENG 428 / ENAS 968 – Cloud FPGA © Jakub Szefer, Fall 2019

#### **Functions**

• Functions are simpler tasks, useful for synthesizable code

```

@(posedge ck)

case (ir [15:13])

//case expressions, as before

3'b111: acc <= multiply(acc, m [ir [12:0]]);

endcase

// code omitted

function signed [12:0] multiply

Function inputs

( input signed [12:0] a,

input signed [15:0] b

and outputs

Output is same as

);

function name

begin: serialMult

Behavioral

reg [5:0] mcnd, mpy;

description of the

function's operation

mpy = b[5:0];

mcnd = a[5:0];

multiply = 0;

repeat (6)

begin

if (mpy[0])

multiply = multiply + {mcnd, 6'b000000};

multiply = multiply >> 1;

mpy = mpy >> 1;

end

end

```

// code omitted

EENG 428 / ENAS 968 – Cloud FPGA © Jakub Szefer, Fall 2019

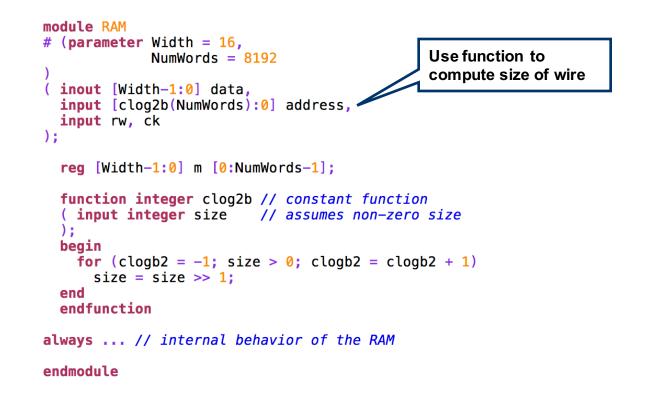

#### **Constant Functions**

Constant functions are just functions, but inputs come from parameters or local parameters and are not values of wires or registers

#### Structural View, Rules of Scope, and Hierarchical Names

#### **Structural View**

- Tasks and functions help to organize the behavioral models

- Modules help to build hierarchical designs

- All three help to design structure of the system

- Progressively can implement more detailed design

- Begin by using \* for multiple

- Finish by writing gate-level description of the multiplier unit

- Behavioral modeling helps to get the design started more quickly

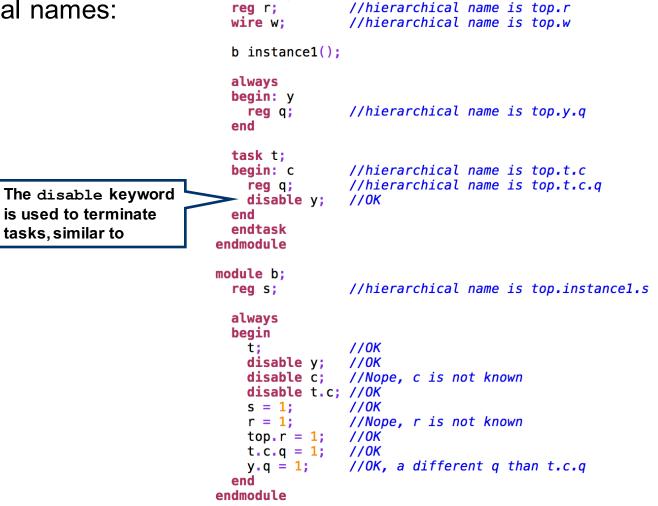

#### **Rules of Scope and Hierarchical Names**

- Module names are known globally across the whole design in Verilog

- Each module instance requires a unique instance name

- Identifiers for modules, tasks, functions, and named begin-end blocks are allowed to be forward referencing and thus may be used before they have been defined

- Forward referencing is not allowed with register and net accesses

- If you forget to declare a variable, or declare variable after it is used, synthesis tools may automatically declare it as a wires leading to errors about double declaration or conflicts

- Each entity in the design can be accessed through hierarchy of names

- Top entity is usually top

- Use dot to specify hierarchy, e.g., top.abc.xyz may mean module xyz inside abc inside top

## **Example of Rules of Scope and Hierarchical Names**

Textbook example of hierarchical names:

module top;

EENG 428 / ENAS 968 – Cloud FPGA © Jakub Szefer, Fall 2019

1. Donald E. Thomas and Philip R. Moorby. " The Verilog Hardware Description Language, Fifth Edition." Springer. 2002